Digital Systems Design

COURSE NOTES

Aykhan Ahmadzada Koç University

#### © 2025 AYKHAN AHMADZADA

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopying, recording, or otherwise—without prior written permission from the author.

This work is a personal academic compilation created for educational purposes as part of the ELEC205 (Digital System Design) course at Koç University.

Compiled in Istanbul, Turkey.

# ELEC205

- **1. Introduction to Digital Devices**

- 2. Binary numbers, Unsigned addition/subtraction, Two's complement system

- **3**. Multiplication, Division, and Binary-Coded Decimal in Digital Systems

- **4.** Combinational Digital Systems and Boolean Algebra

- **5. Boolean Function Representations and Circuit Optimization**

- **8** 6. Karnaugh Maps and Boolean Function Optimization

- **7. Karnaugh Map Simplification & Prime Implicant Optimization**

- 8. Digital Logic Optimization and Karnaugh Map Techniques

- 9. Exclusive OR, Adder Circuits, and Digital Addition

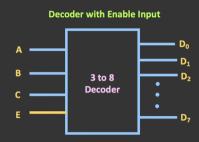

- **10. Digital Decoders: Architecture, Expansion, and Applications in Circuit Design**

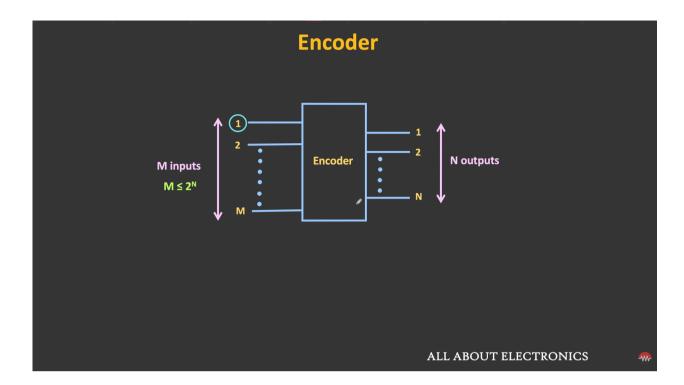

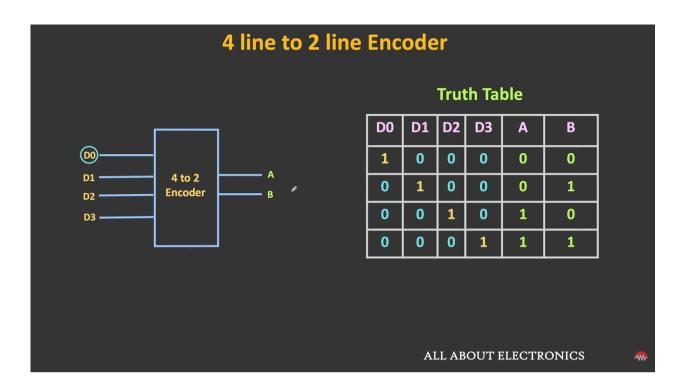

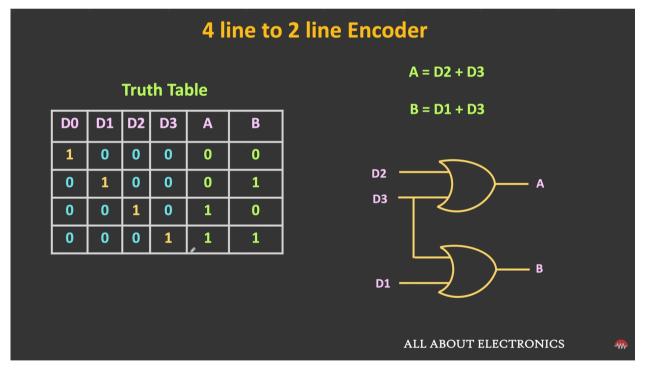

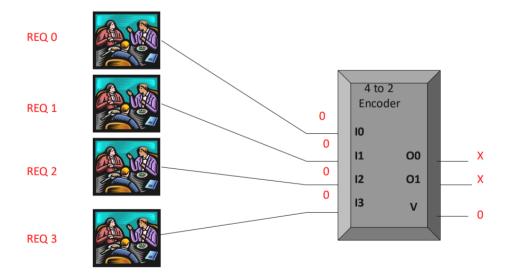

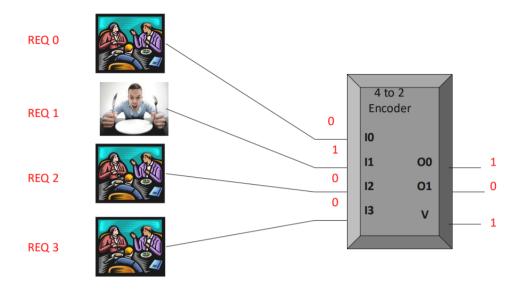

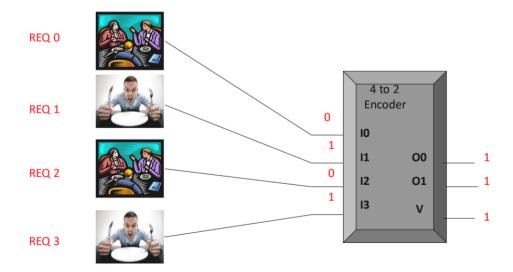

- **11. Encoders, Selecting Functions and Multiplexers**

- **12. Solutions for Midterm Sample Questions**

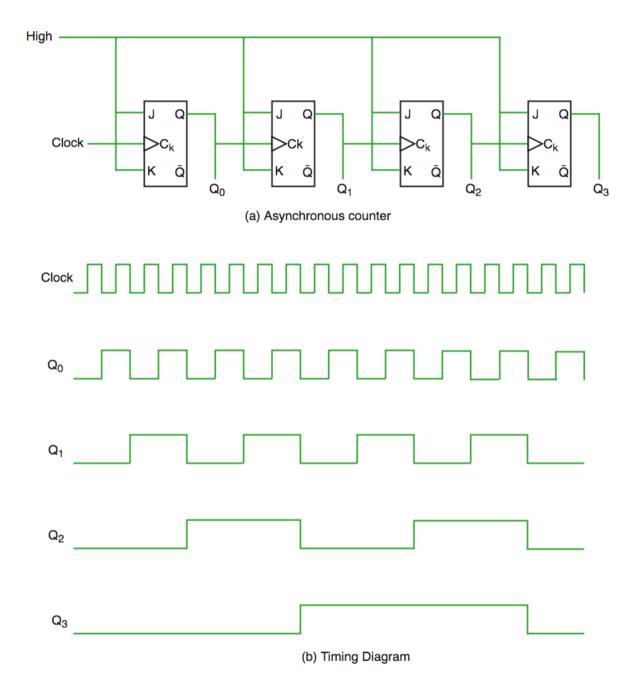

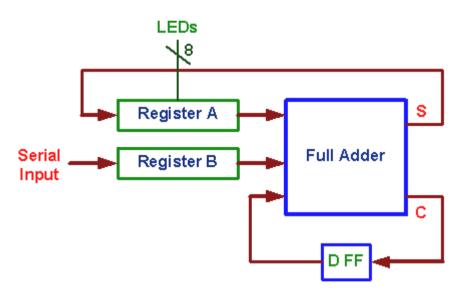

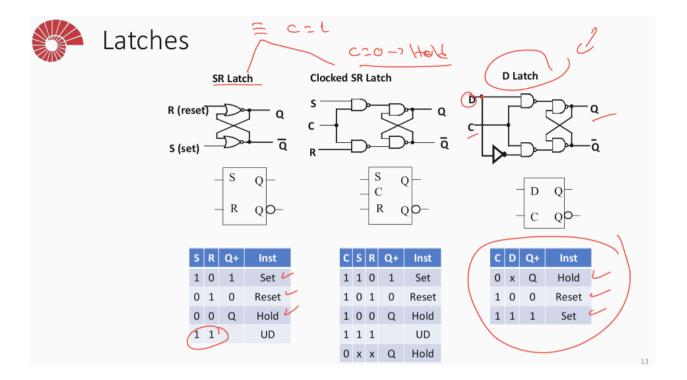

- **\$ 13. Sequential Logic and Memory**

- **14. Flip-Flops & Sequential Circuit Analysis**

- **15. Finite State Machines: State Diagrams, Models, and Representations**

- **16. FSM Design & Sequence Detection**

- **\$ 17. State Assignment & Minimization**

- **18. Sequential-Circuit Fundamentals & Flip-Flops**

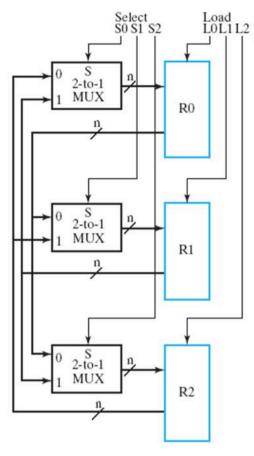

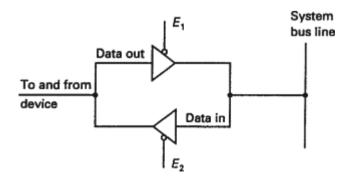

- **19. Registers & Bus-Based Transfer Structures**

- **20. Registers and Register Transfer Operations**

- **21. Counters, Shift Registers, and Serial Transfer**

- **22. Programmable Computer and Control Unit**

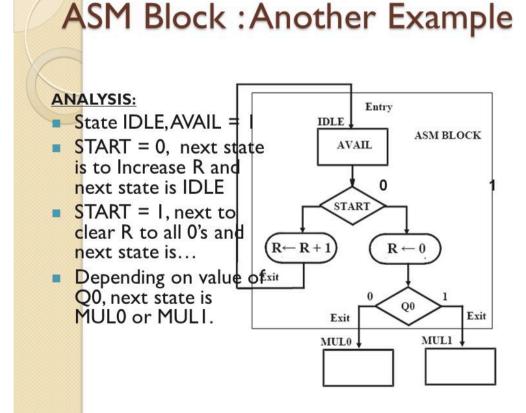

- **23.** Algorithmic State Machines and ASM Design

- **24. Design Examples**

- **25. Final Exam Review**

# 1. Introduction to Digital Devices

**Objective**: This note covers the topics from **ELEC 205** Week 1 (Slides 9–36), focusing on the transition from analog to digital systems, fundamental digital devices, and an introductory multiplexer (MUX) design example.

# What is Digital? (Analog vs. Digital)

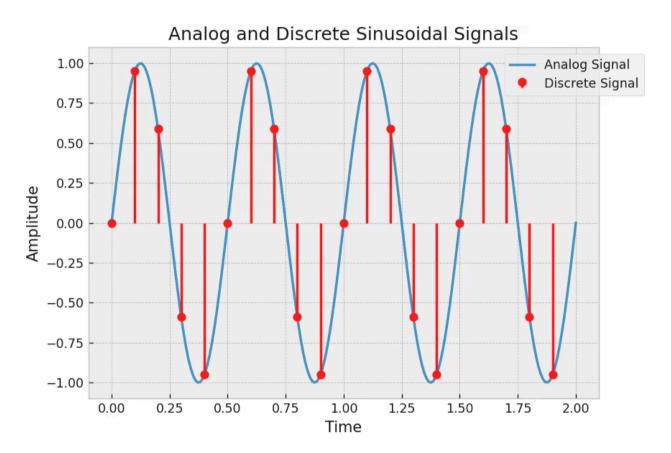

Digital systems operate on discrete (individually separate and distinct) signals—typically 0s and 1s—in contrast to the continuous range of analog signals. Understanding the interplay between analog and digital is crucial for modern electronic design.

#### Analog vs. Digital Signals

Real-world signals (such as sound waves) are analog and vary continuously. Digital systems sample these signals at discrete intervals.

**(NYQUIST-SHANNON) SAMPLING THEOREM:** If you sample an analog signal at a rate at least twice its highest frequency component, you can fully reconstruct it from these samples. This minimum sampling rate is called the **Nyquist rate.**

**Frequency:** the number of waves that pass by each second, and is measured in Hertz (Hz).

Physical Storage of 0s and 1s

- Bumps on a CD

- Magnetic domains on a hard disk

- Charge in flash memory transistors

- Flip-flops in integrated circuits

Although hardware at the transistor level is analog, digital abstraction ensures signals are treated as purely "HIGH" (1) or "LOW" (0).

#### **Everyday Examples**

- **Analog TV vs. Digital TV**: Digital TV encodes images as binary data frames, while analog TV uses continuously modulated waves.

- CD Audio: Music is stored as samples at 44.1 kHz, each sample represented by bits.

- Cell Phones: Convert voice to digital signals, process internally, then convert back to analog for playback.

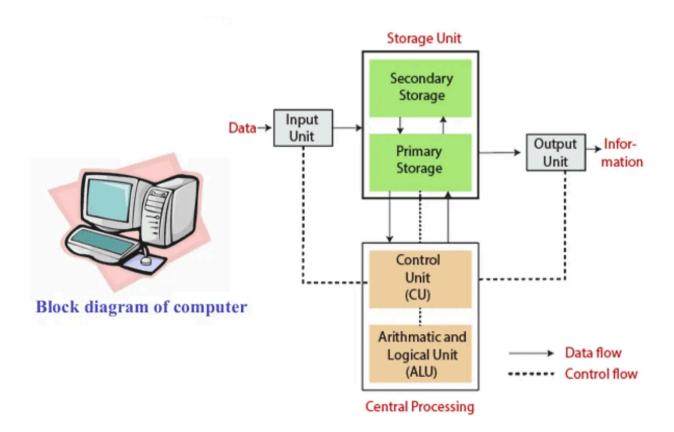

# **Digital Systems and Applications**

A **digital system** takes binary data as input, performs logic or arithmetic on it, and outputs new binary data. In practice, an ADC (Analog-to-Digital Converter) fronts the system for input, and a DAC (Digital-to-Analog Converter) follows it for output.

#### **Examples of Applications**

- 1. **Gaming Consoles**: Controller inputs are converted to binary, processed by a CPU/GPU, then sent to a display or speakers (digital or analog output).

- 2. **Personal Computers**: Keyboard and mouse signals are interpreted digitally, processed, and output to a monitor or speaker.

- 3. **Cell Phones**: Convert audio to packets of digital data, process and store them, and finally reproduce audio signals.

#### GAMING

# **Benefits of Digital Systems**

#### **BENEFITS:**

- **Reproducibility**: Digital copying does not degrade quality.

- **Ease of Design**: Logical operations (AND, OR, NOT) are simpler conceptually than continuously variable signals.

- **Flexibility & Programmability**: Can be updated/reconfigured using firmware or hardware description languages (HDLs).

- **Speed**: Modern transistors switch in picoseconds, enabling rapid processing.

- **Economy**: Highly complex functionality on tiny chips.

- **Advancing Technology**: Each new generation of semiconductor technology brings higher performance at lower cost.

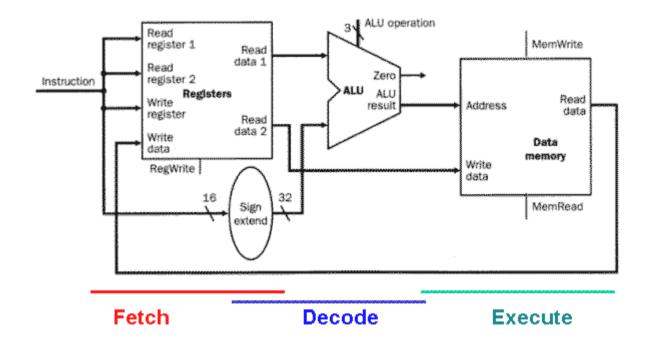

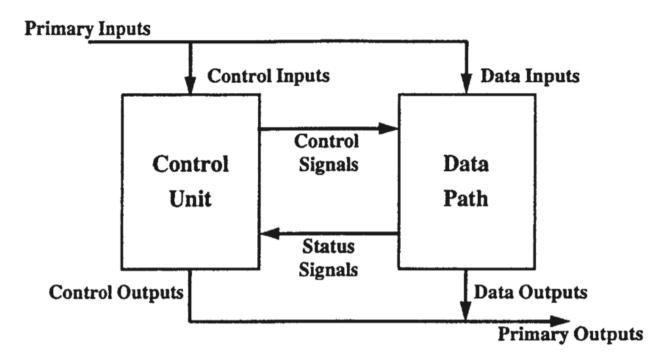

# **Digital Computer Architecture**

A basic digital computer typically includes:

- **Memory**: Stores both instructions and data.

- **Datapath**: Executes arithmetic and logical operations.

- Control Unit: Directs the flow of data and orchestrates operations.

- CPU: Combines control and datapath, often featuring a Floating Point Unit (FPU)

for specialized arithmetic and a Memory Management Unit (MMU) for handling

caches and memory addressing.

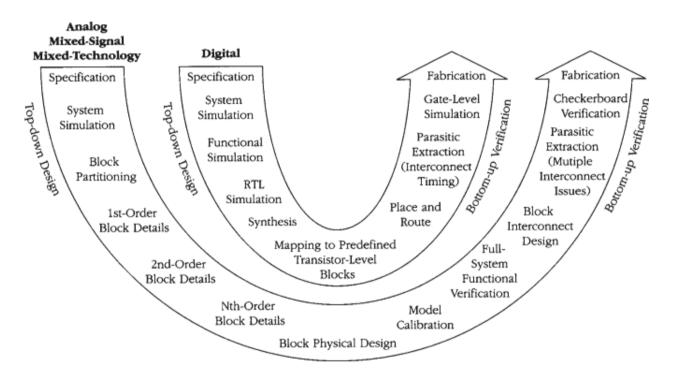

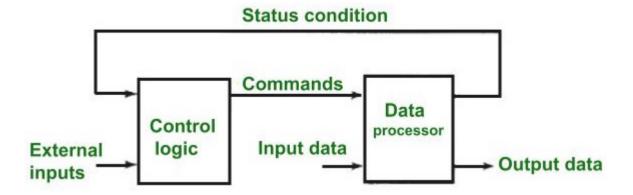

# **Constructing Digital Systems**

**DIGITAL SYSTEM:** Inputs (binary) → Processing (logic or arithmetic) → Outputs (binary)

The high-level design flow involves specifying the required behavior, then transforming it into logical components. Modern workflows use simulators and HDLs to validate designs before hardware fabrication.

# Digital Devices (Gates and Memory)

#### **Basic Gates**

AND, OR, and NOT form the foundational building blocks of any digital logic design. Combinational circuits are built exclusively from these gates or their derivatives.

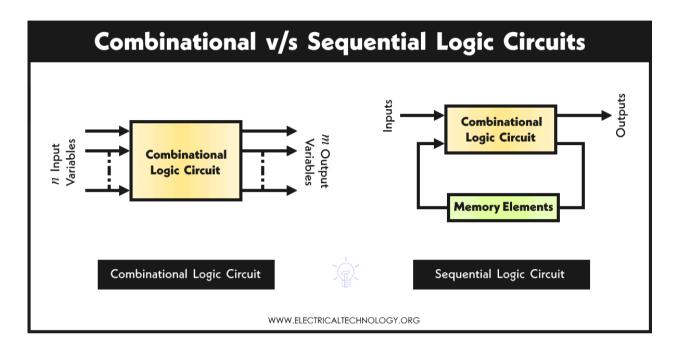

**COMBINATIONAL CIRCUIT:** A circuit whose output depends solely on its current inputs, with no internal storage. **(no memory!)**

#### **Memory Elements**

FLIP-FLOP: A 1-bit storage device that latches data on a clock edge.

**SEQUENTIAL CIRCUIT:** Combines gates and flip-flops so that outputs depend on current inputs and previously stored states (past inputs). **(with memory!)**

Sequential circuits can implement counters, shift registers, and entire finite state machines.

# **Electronic and Software Aspects**

All gates and flip-flops are physically analog (transistors, resistors, capacitors), but operate within defined voltage levels to represent 0 or 1. Designers rely on:

- CAD Tools & Simulators: For schematic-based or HDL-based design entry.

- **HDLs (VHDL, Verilog, SystemVerilog)**: For specifying either the behavior (dataflow/behavioral style) or structure (gate-level) of a design.

**HDL:** VHDL is a hardware description language (HDL) that is used to describe the structure and behavior of digital systems and circuits.

# **Digital Design Levels (MUX Example)**

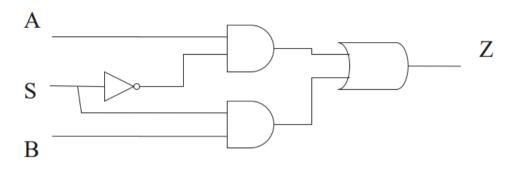

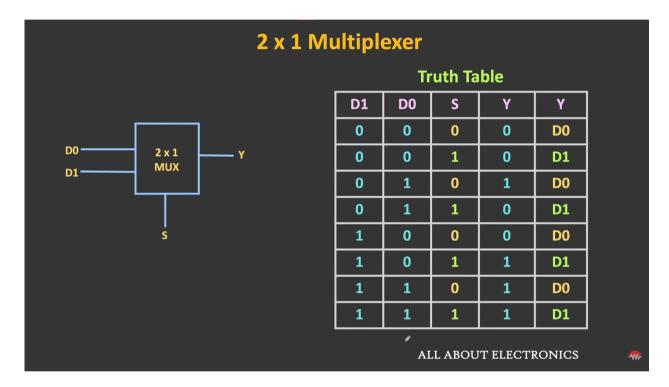

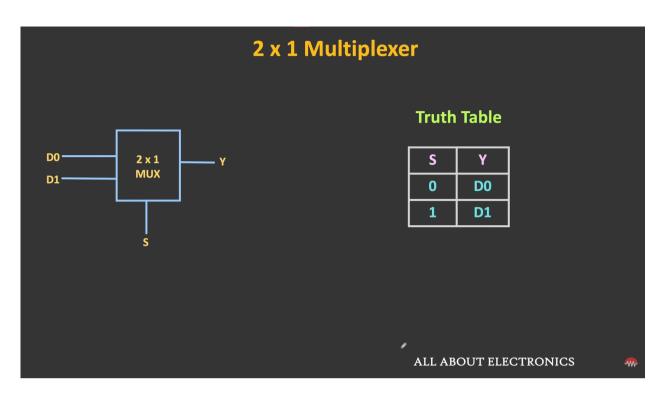

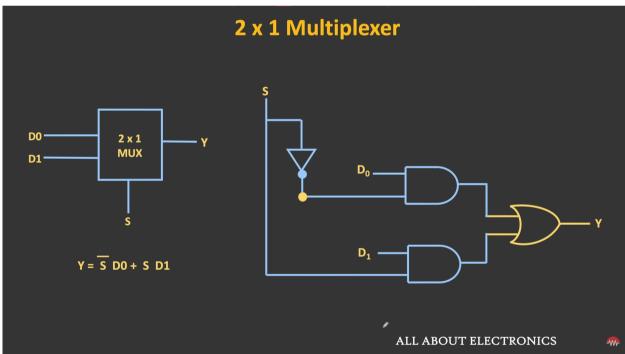

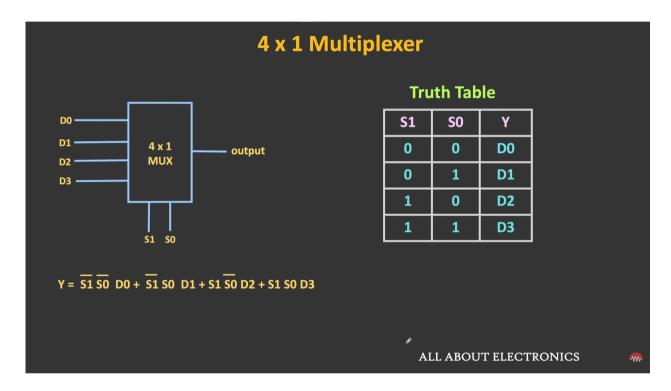

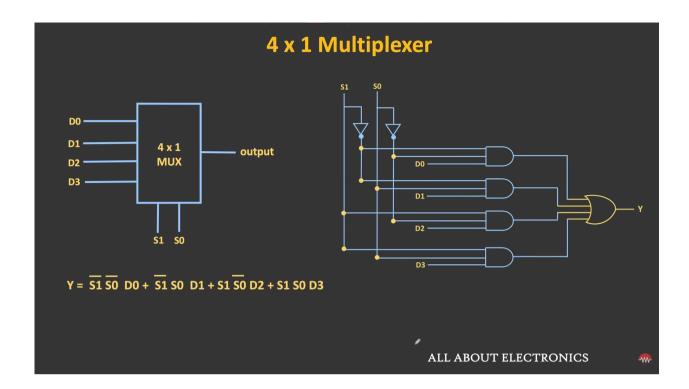

#### Multiplexer (2-Input MUX)

A multiplexer (MUX) selects one of its inputs to pass through to the output.

**MULTIPLEXER:** A device that outputs one of several data inputs, controlled by a select signal.

# Multiplexers

- >> It is combinational circuit that selects binary information from one of many input lines and directs it to o/p line.

- >> It is simply a DATA SELECTOR

# 118 Digital Electronics

#### **Truth Table**

| S | Α | В | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

When S = 0, Z = A. When S = 1, Z = B.

#### **Gate-Level Diagram**

# • Gate level logic diagram (schematic):

# HDL (VHDL) Example

```

library IEEE;

use IEEE.std_logic_1164.all;

entity V1mux is

port(

A, B, S : in STD_LOGIC;

Z : out STD_LOGIC

);

end V1mux;

architecture V1mux_arch of V1mux is

begin

-- Dataflow style

Z <= A when S = '0' else B;

end V1mux_arch;</pre>

```

This example demonstrates how designers can describe hardware behavior at a higher level. A gate-level variant would instantiate specific AND, OR, and NOT components

# Why Digital Wins: Precision, Stability, and Efficiency

Even though the physical world operates in an analog way—like sound waves, temperature changes, and light brightness—modern technology increasingly relies on digital systems because they offer precision, reliability, and efficiency that analog cannot always provide.

Analog signals are **continuous** and can take infinite values, but they are also **vulnerable** to noise and degradation. That's why, when you listen to an analog radio, you sometimes hear that "dzzzzzz" noise—it's interference corrupting the signal. Over time, copying an analog signal (like a cassette tape) causes it to lose quality, whereas digital signals remain **unchanged** no matter how many times they are copied.

However, some things still feel analog, even in digital systems. For example, when you adjust the brightness of your iPhone's flashlight, it seems like a smooth change, but the LED is actually flickering on and off rapidly using **Pulse Width Modulation (PWM)**. This is how digital systems simulate the behavior of analog while still keeping the benefits of binary operation.

One key feature of digital devices is that they either work perfectly or not at all. Since digital signals are based on 1s and 0s, there's no gradual loss of quality. A radio station using digital transmission either delivers a **clear signal** or nothing at all—there's no static like in analog radio. The same applies to digital files, which either open **perfectly** or become completely unreadable if corrupted.

In the end, digital doesn't replace analog completely—it refines and optimizes it. We still live in an analog world, but digital technology helps us process, store, and transmit information more efficiently, making it clearer, more reliable, and easier to manipulate.

### **Self Test**

Self-Test: Lecture 1

# 2. Binary numbers, Unsigned addition/subtraction, Two's complement system

**Objective**: This note covers the topics from **ELEC 205** Week 1 (Slides 37–57), focusing on number systems (binary, octal, hexadecimal), two's complement, and various binary arithmetic operations.

# **Number Systems**

A number system defines how numeric values are represented. In digital electronics, we commonly use **binary** (base 2), but other bases such as **octal** (base 8) and **hexadecimal** (base 16) are also helpful.

| Numbering System |             |                                 |  |

|------------------|-------------|---------------------------------|--|

| System           | Base Digits |                                 |  |

| Binary           | 2           | 0, 1                            |  |

| Octal            | 8           | 0,1,2,3,4,5,6,7                 |  |

| Decimal          | 10          | 0,1,2,3,4,5,6,7,8,9             |  |

| Hexadecimal      | 16          | 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F |  |

#### Octal and Hexadecimal Numbers

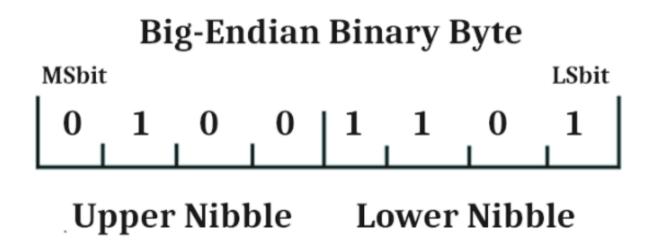

Octal (base 8) digits cover 0 to 7, each corresponding to three bits in binary. Hexadecimal (base 16) digits span 0 to 9 and A to F, each corresponding to four bits in binary. Converting between binary and hex is straightforward by grouping bits in fours; octal uses groupings of three bits.

**OCTAL DIGIT:** Uses 3 bits (e.g.,  $101_2 = 5_8$ ).

**HEXADECIMAL DIGIT**: Uses 4 bits (e.g.,  $1010_2 = A_{16}$ ).

These systems give concise shorthand for large binary strings, useful in debugging, memory addresses, and processor instructions.

# **Positional Number System Conversions**

Numbers in any base r are interpreted by positional notation. For digits to the left of the radix point, powers of r increase from right to left; for digits to the right, powers of r are negative.

- 1. **Base-r to Decimal**: Multiply each digit by  $r^{

m position}$  and sum the results.

- 2. **Decimal to Base-r**: Repeatedly divide by r, keep track of remainders, and reverse them at the end.

**EXAMPLE**: Converting  $179_{10}$  to binary:

- 1.  $179 \div 2 = 89$  remainder 1

- 2.  $89 \div 2 = 44$  remainder 1

- 3.  $44 \div 2 = 22$  remainder 0

- 4.  $22 \div 2 = 11$  remainder 0

- 5.  $11 \div 2 = 5$  remainder 1

- 6.  $5 \div 2 = 2$  remainder 1

- 7.  $2 \div 2 = 1$  remainder 0

- 8.  $1 \div 2 = 0$  remainder 1 (MSB)

Reverse remainders  $\rightarrow 10110011_2$ .

#### **Additional Example**

- Convert  $300_{10}$  to octal:

- $\circ$  300  $\div$  8 = 37 remainder 4

- $\circ$  37  $\div$  8 = 4 remainder 5

- $\circ \ 4 \div 8 = 0$  remainder 4 (MSB)

- $\circ$  Result:  $454_8$ .

# **Addition and Subtraction of Binary Numbers**

Binary addition and subtraction are analogous to decimal, except the base is 2.

**BINARY ADDITION:**  $1+1=10_2$ . If both bits are 1, produce a sum bit of 0 and carry out 1.

**BINARY SUBTRACTION**: 1 - 1 = 0, but 0 - 1 requires borrowing from a more significant bit.

#### **Additional Examples**

• **Addition**:  $1011_2$  (11 in decimal) +  $1000_2$  (8 in decimal) =  $10011_2$  (19 in decimal)

Addition

101111000

X 190 10111110

Y 141 10001101

\_\_\_\_<sup>T</sup>\_\_\_\_\_

X+Y 331 101001011

| Cin/bin | X | Y | Cout | S | Bout | D |

|---------|---|---|------|---|------|---|

| 0       | 0 | 0 | 0    | 0 | 0    | 0 |

| 0       | 0 | 1 | 0    | 1 | 1    | 1 |

| 0       | 1 | 0 | 0    | 1 | 0    | 1 |

| 0       | 1 | 1 | 1    | 0 | 0    | 0 |

| 1       | 0 | 0 | 0    | 1 | 1    | 1 |

| 1       | 0 | 1 | 1    | 0 | 1    | 0 |

| 1       | 1 | 0 | 1    | 0 | 0    | 0 |

| 1       | 1 | 1 | 1    | 1 | 1    | 1 |

- Subtraction:  $1011_2$  (11 in decimal)  $1000_2$  (8 in decimal) =  $0011_2$  (3 in decimal)

- Binary subtraction: (borrow, difference bits)

| B <sub>out</sub><br>Minuend | X       | 229 | 001111100<br>11100101 |

|-----------------------------|---------|-----|-----------------------|

| Subtrahend                  | Υ       | 46  | 00101110              |

| Difference 2                | <br>X-Y | 183 | 10110111              |

| Cin/bin | X | Y | Cout | S | Bout | D |

|---------|---|---|------|---|------|---|

| 0       | 0 | 0 | 0    | 0 | 0    | 0 |

| 0       | 0 | 1 | 0    | 1 | 1    | 1 |

| 0       | 1 | 0 | 0    | 1 | 0    | 1 |

| 0       | 1 | 1 | 1    | 0 | 0    | 0 |

| 1       | 0 | 0 | 0    | 1 | 1    | 1 |

| 1       | 0 | 1 | 1    | 0 | 1    | 0 |

| 1       | 1 | 0 | 1    | 0 | 0    | 0 |

| 1       | 1 | 1 | 1    | 1 | 1    | 1 |

- Use binary subtraction to compare numbers.

- If X-Y produces a borrow out at the most significant bit, then X is less than Y.

# **Representation of Negative Numbers**

Various methods can represent signed integers in binary:

SIGNED-MAGNITUDE: A sign bit plus magnitude bits.

**ONE'S COMPLEMENT:** Flip (invert) all bits to represent negative.

TWO'S COMPLEMENT: Invert bits and then add 1 for negative.

Two's complement is most common because it simplifies hardware for addition/subtraction.

# Signed-Magnitude System

The most significant bit (MSB) is the sign: 0 for positive, 1 for negative. The rest of the bits store the magnitude. Though intuitive, arithmetic operations are more complex compared to two's complement.

# Signed-Magnitude System

• MSB: sign bit, 0: plus, 1: minus

$$01010101_2 = +85_{10}$$

$11010101_2 = -85_{10}$

$01111111_2 = +127_{10}$   $11111111_2 = -127_{10}$

$00000000_2 = +0_{10}$   $10000000_2 = -0_{10}$

- n-bit signed integer lies within  $-(2^{n-1}-1)$  through  $+(2^{n-1}-1)$  with two representations of zero.

# **Diminished Radix Complement System**

(r-1)'**S COMPLEMENT:** For an n-digit number N,  $(r^n-1)-N$ . In binary (r=2), this is one's complement, created by flipping all bits.

The **diminished radix complement system** is a way of representing negative numbers by subtracting a number from the **largest possible value** in a given number system.

- Given a number N in radix r having n digits

- The (r-1)'s complement of N is defined as: (r<sup>n</sup> − 1) N

- For binary, one's complement of N is: (-N) = (2<sup>n</sup> 1) N

# **Complement Number Systems**

Complement systems allow negative numbers to be handled using the same addition logic as positive numbers.

**RADIX COMPLEMENT:** For base r, the complement is  $r^n-N$ . In binary,  $2^n-N$  (two's complement).

- Taking the complement is more difficult than changing the sign, but in complement system add/subt are easier.

- Radix complement of N:  $(-N) + N = r^n \rightarrow (-N) = r^n N$ where N is an n-digit number

- If N is between 1 and  $r^n$ -1 then (-N) is between  $r^n$ -1 and  $r^n$  ( $r^n$ -1) = 1

- When N=0, (-N) is r<sup>n</sup>, which is (n+1) digits, hence (-N) is also 0.

# Two's Complement System

- 1. Invert (one's complement).

- 2. Add 1.

**TWO'S COMPLEMENT:** -N is  $2^n-N$ . This avoids having two representations for zero and simplifies arithmetic.

- Range for n bits:  $-2^{n-1}$  through  $+2^{n-1}-1$ .

- Radix complement for binary numbers

N: n bit binary number

$$(-N) = 2^n - N = (2^{n}-1) - N + 1$$

$$17_{10} = 00010001_2$$

$0000_2$   $11101110$   $1111$   $+$   $11101111_2 = -1710$   $10000_2$

#### **Additional Example**

- Convert -6 to 8-bit two's complement:

- 1. +6 = 0000 0110.

- 2. Flip bits  $\rightarrow$  1111 1001.

- 3. Add 1  $\rightarrow$  1111 1010 (final representation of -6).

# **Signed Number Systems**

#### **SIGNED NUMBER SYSTEMS:**

- Signed-Magnitude (clear sign bit, complex arithmetic)

- One's Complement (invert bits for negative)

- Two's Complement (dominant standard, single zero, consistent addition/subtraction)

#### Let's consider n-bit binary number: $A = a_{n-1} a_{n-2} ... a_1 a_0$

- Sign-Magnitude System (-(2<sup>n-1</sup>-1) to (2<sup>n-1</sup>-1))

- Sign:  $a_{n-1}$  (MSB);  $a_{n-1}$  = 0 positive,  $a_{n-1}$  = 1 negative

- Magnitude: a<sub>n-2</sub> ...a<sub>1</sub> a<sub>0</sub>

- One's Complement System (-(2<sup>n-1</sup>-1) to (2<sup>n-1</sup>-1))

- Negation is represented with bitwise NOT

- $(-A) = (2^{n}-1) A = a'_{n-1} a'_{n-2} ... a'_{1} a'_{0}$ ; (+1=0001, -1=1110)

- Two's Complement System (-(2<sup>n-1</sup>) to (2<sup>n-1</sup>-1))

- Decimal value of A is represented as:

•

$$A = -2^{n-1}a_{n-1} + 2^{n-2}a_{n-2} + ... + 2^{1}a_{n-1} + 2^{0}a_{n-2}$$

- Satisfies (-A) + A =  $2^n$   $\rightarrow$  (-A) =  $2^n$  - A =  $(2^n - 1)$  - A + 1

# 3-Bit Number Examples

When n=3, two's complement ranges from -4 ( $100_2$ ) to +3 ( $011_2$ ).

| Bits | Unsigned | Signed<br>Magnitude | One's<br>Complement | Two's<br>Complement |

|------|----------|---------------------|---------------------|---------------------|

| 000  | 0        | 0                   | 0                   | 0                   |

| 001  | 1        | 1                   | 1                   | 1                   |

| 010  | 2        | 2                   | 2                   | 2                   |

| 011  | 3        | 3                   | 3                   | 3                   |

| 100  | 4        | -0                  | -3                  | -4                  |

| 101  | 5        | -1                  | -2                  | -3                  |

| 110  | 6        | -2                  | -1                  | -2                  |

| 111  | 7        | -3                  | -0                  | -1                  |

#### **Additional Example**

| Binary | Unsigned | Signed-<br>Magnitude | One's<br>Complement | Two's<br>Complement |

|--------|----------|----------------------|---------------------|---------------------|

| 100    | 4        | -0                   | -3                  | -4                  |

| 101    | 5        | -1                   | -2                  | -3                  |

| 110    | 6        | -2                   | -1                  | -2                  |

| 111    | 7        | -3 (or -0)           | -0 (or -0)          | -1                  |

# Addition in Two's Complement

Perform regular binary addition. A negative operand is already stored in two's complement form.

**EXAMPLE:** -3+1 in 4-bit two's complement

- $-3 \rightarrow 1101_2$

- $+1 \rightarrow 0001_2$

- Sum =  $1110_2$  (-2 in decimal)

Check for **overflow** when results exceed  $[-2^{n-1}, 2^{n-1}-1]$ .

#### **Additional Example**

- -4 + 2 in 4-bit:

- $\circ$   $-4 = 1100_2$

- $\circ \ \ 2 = 0010_2$

- Sum =  $1110_2 \rightarrow (-2)$

# Subtraction in Two's Complement

To subtract Y from X, compute  $X+\left( -Y\right)$ . Negative numbers are formed via two's complement.

#### **Additional Example**

- 5-6 in 4-bit:

- $\circ$  5 = 0101<sub>2</sub>

```

\circ 6 = 0110<sub>2</sub>

```

$$\circ$$

$-6 = 1001_2 + 1 = 1010_2$

$$\circ$$

0101 + 1010 = 1111<sub>2</sub> = (-1)

# 1. Unsigned System

- Represents only non-negative numbers.

- All bits contribute to the numerical value.

- The range is from  ${\bf 0}$  to  $2^n-1$  for an n-bit system.

- Example (4-bit system):

- o Binary: 0000 to 1111

- o Decimal equivalents: 0 to 15

There is no concept of negative numbers in an unsigned system.

# 2. Signed Systems (Different Complement Methods)

#### A. Signed Magnitude

- The leftmost bit (MSB) is the sign bit.

- **Ø** = positive

- o 1 = negative

- The remaining bits represent the magnitude.

- The range for an n-bit system is  $-(2^{n-1}-1)$  to  $+(2^{n-1}-1)$ .

- Example (4-bit system):

- 0 0111 = +7

- 0 1111 = -7

- **Problem:** Two representations of zero ( and and ), which makes arithmetic operations complicated.

## **B. One's Complement (Diminished Radix Complement)**

- Negative numbers are represented by flipping all bits.

- The range for an n-bit system is  $-(2^{n-1}-1)$  to  $+(2^{n-1}-1)$ .

- Example (4-bit system):

- 0 0111 = +7

- O 1000 = -7

- 0 0000 = +0

- 1111 = -0 (**Problem:** Two zeros, which complicates arithmetic)

#### C. Two's Complement (Radix Complement)

- Negative numbers are found by **flipping all bits and adding 1**.

- $\circ \hspace{0.1in}$  The range for an n-bit system is  $-2^{n-1}$   $\operatorname{{f to}}$   $+(2^{n-1}-1)$  .

- Example (4-bit system):

- 0 0111 = +7

- 0 1001 = -7

- Arithmetic works smoothly, making it the **standard for modern computers**.

# Key Differences Between Signed and Unsigned Systems

| Feature                    | Unsigned                | Signed<br>Magnitude     | One's<br>Complement     | Two's<br>Complement     |

|----------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| MSB Role                   | Part of the magnitude   | Sign bit (0 = +, 1 = -) | Sign bit (0 = +, 1 = -) | Sign bit (0 = +, 1 = -) |

| Range (4-bit)              | 0 to 15                 | -7 to +7                | -7 to +7                | -8 to +7                |

| Negative<br>Representation | Not supported           | Flip MSB                | Flip all bits           | Flip all bits and add 1 |

| Zero<br>Representation     | 0000 (0 only)           | (-0) (+0), 1000         | (-0) (+0), 1111         | eeee (only one zero)    |

| Arithmetic<br>Simplicity   | Simple but no negatives | Complex                 | Complex (double zero)   | Efficient<br>(modern    |

standard)

- **Unsigned numbers** are simple but cannot represent negatives.

- **Signed numbers** use different methods, with **two's complement being the most practical and widely used** because it avoids double-zero issues and simplifies arithmetic.

- Diminished Radix Complement (One's, Nine's, Three's, etc.)

- Found by subtracting from the highest possible value minus 1.

- Has two representations of zero.

- Radix Complement (Two's, Ten's, Four's, etc.)

- Found by subtracting from the full radix power.

- Has **only one zero representation**, making it more practical for arithmetic.

#### **Complement Comparison Table**

| Base           | Diminished Radix<br>Complement | Formula      | Radix<br>Complement  | Formula  |

|----------------|--------------------------------|--------------|----------------------|----------|

| Binary (2)     | One's Complement               | $(2^n-1)-N$  | Two's<br>Complement  | $2^n-N$  |

| Decimal (10)   | Nine's Complement              | $(10^n-1)-N$ | Ten's<br>Complement  | $10^n-N$ |

| Quaternary (4) | Three's<br>Complement          | $(4^n-1)-N$  | Four's<br>Complement | $4^n-N$  |

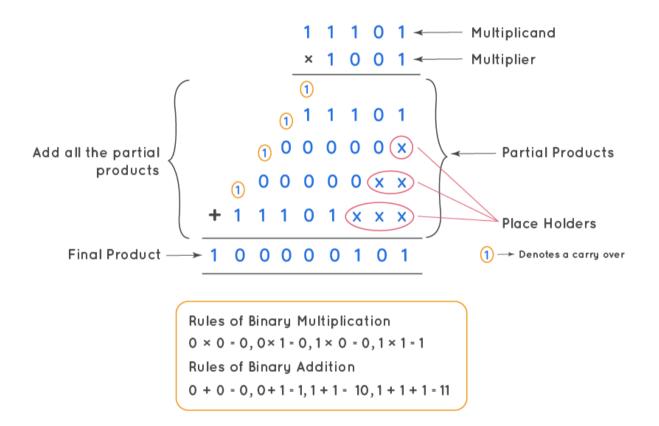

# **Binary Multiplication**

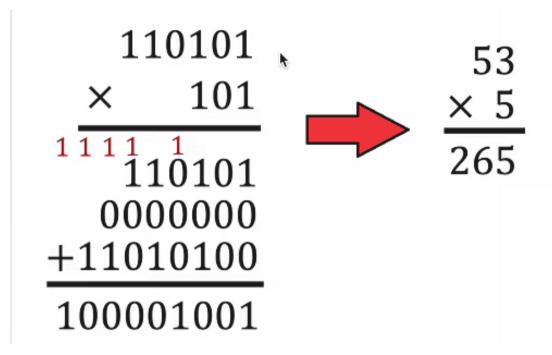

Unsigned multiplication uses **shift-and-add**. Two's complement multiplication extends this approach while managing sign bits.

**BINARY MULTIPLICATION:** Multiply partial products, each shifted by the position of the bit in the multiplier.

#### **Additional Example**

- $3 \times 2$  in binary (unsigned):

- $\circ$  3 = 0011<sub>2</sub>

- $\circ 2 = 0010_2$

- Multiply partial products:

- $1 \text{ (LSB of 2)} \rightarrow 0011$

- Next bit is  $0 \rightarrow 0000$ , shifted

- Sum =  $0110_2$  (6 in decimal)

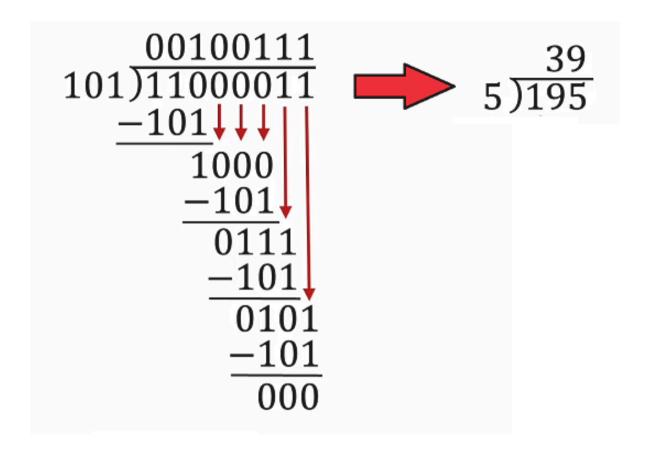

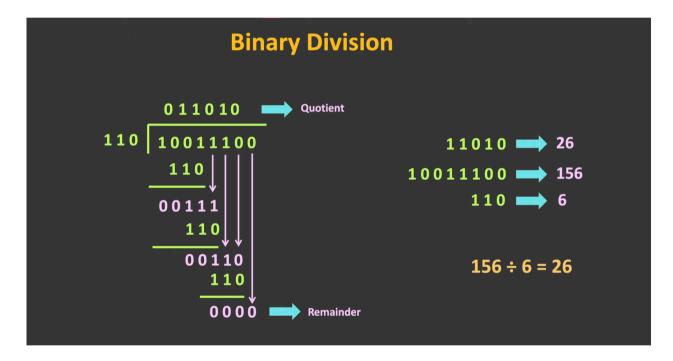

# **Binary Division**

Binary division often uses **shift-and-subtract**. For signed numbers, adjust for sign before or after the division.

#### **Additional Example**

- $14 \div 2$  in binary:

- $\circ 14 = 1110_2, 2 = 0010_2.$

- $\circ$  Perform repeated shifting and subtracting until the final quotient is found (  $0111_2)$  = 7, with remainder 0.

# **Binary-Coded Decimal (BCD)**

BCD encodes each decimal digit (0–9) into a 4-bit binary code (0000 to 1001). Any 4-bit pattern above 1001 is invalid in standard BCD.

BCD: 0111 (7) is valid, 1010 (10) is not valid for a single decimal digit.

#### **BCD** Addition

If a 4-bit sum exceeds 9 ( $1001_2$ ), add 6 ( $0110_2$ ) to adjust the digit and manage any carry.

#### **Additional Example**

- Add **44** and **89** in BCD:

- $\circ$  44  $\rightarrow$  0100 0100

- 89 → 1000 1001

- $\circ$  Initial sum  $\rightarrow 100111111$  (not corrected)

- $\circ$  Adjust each nibble > 1001 by adding 0110

- $\circ$  Final correct BCD result = 133 (1 3 3 =  $0001\ 0011\ 0011$  in BCD)

#### Why is BCD (Binary-Coded Decimal) Used?

BCD (Binary-Coded Decimal) is used primarily in applications where decimal precision is important. Instead of storing numbers in pure binary, BCD represents each decimal digit separately using a 4-bit binary equivalent. BCD is not memoryefficient. It wastes storage compared to pure binary. BCD is easy to encode and decode.

#### **Self Test**

**Self-Test: Lecture 2**

# 3. Multiplication, Division, and Binary-Coded Decimal in Digital Systems

This note covers the full range of arithmetic operations in digital systems, including both multiplication and division for signed and unsigned numbers, as well as an in-depth look at Binary-Coded Decimal (BCD).

# **Multiplication in Digital Systems**

Multiplication in digital systems can be performed on both unsigned and signed numbers. The underlying mechanism is typically based on the shift-and-add algorithm.

#### **Unsigned Multiplication**

For unsigned numbers, multiplication is conceptually similar to decimal multiplication but performed in binary. The basic idea is:

- Shift: For each bit in the multiplier, shift the multiplicand by the appropriate number of positions.

- Add: Sum the shifted multiplicands where the corresponding bit of the multiplier is 1.

**Example:** Multiply  $1011_2$  (11 in decimal) by  $0101_2$  (5 in decimal).

- Multiply each bit of the multiplier by the multiplicand and shift accordingly.

- Add the resulting partial products to obtain the final product.

#### **Binary Multiplication**

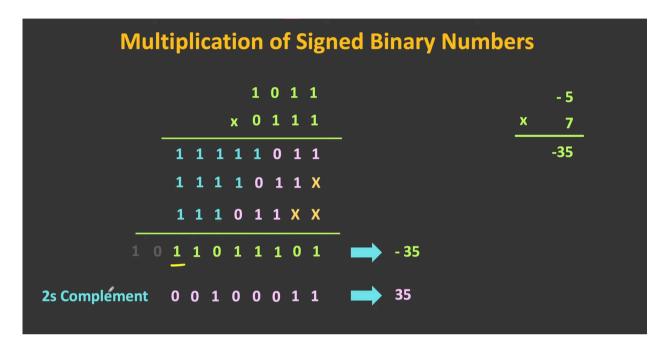

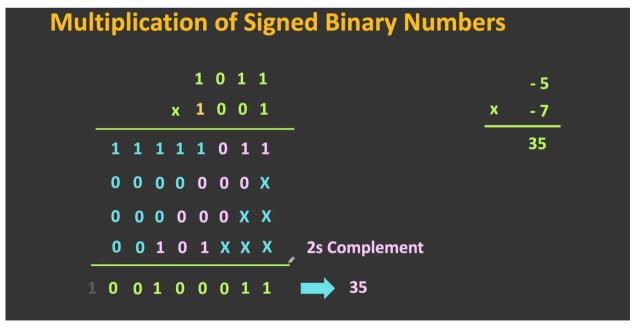

#### **Signed Multiplication**

For signed numbers, the typical method is to use two's complement representation. The same shift-and-add procedure is applied, but extra care is needed to:

- **Sign Extend:** Ensure that when shifting, the sign bit is correctly extended.

- Adjust: Interpret the final result as a two's complement number.

- **Two's Complement Correction:** If the multiplicand is negative, the last partial product must be converted to its two's complement form to maintain correctness.

**Key Point:** The algorithm for signed multiplication is similar to unsigned multiplication, but the hardware or software must handle sign bits appropriately, ensuring that negative partial products are correctly processed using two's complement conversion when necessary.

# 2. Division in Digital Systems

Division is the inverse of multiplication and, like multiplication, is performed differently for unsigned and signed numbers.

#### **Unsigned Division**

Unsigned division is generally carried out by a shift-and-subtract method:

- **Shift:** Align the divisor with the dividend's most significant bit.

- **Subtract:** Subtract the divisor (or its shifted version) from the dividend if it fits; record a 1 in the quotient.

- Repeat: Continue the process by shifting and subtracting until all bits are processed.

**Example:** Dividing a binary number by another using repeated subtraction and shifts.

#### **Signed Division**

For signed division using two's complement representation, the algorithm typically involves:

- **Determining the Sign:** The sign of the result is the product of the signs of the dividend and divisor.

- **Converting to Unsigned:** Temporarily convert both numbers to their absolute (unsigned) values.

- Performing Division: Use the unsigned division algorithm.

- **Restoring the Sign:** Apply the appropriate sign to the quotient.

**Considerations:** Care must be taken to handle cases like division by zero and the edge case where the dividend is the minimum representable value.

# 3. Binary-Coded Decimal (BCD)

Binary-Coded Decimal (BCD) is a method of representing decimal numbers in which each digit is stored as its own 4-bit binary number. This is especially useful in applications where decimal precision is critical (e.g., financial calculations).

#### Representation

- **Standard BCD:** Each decimal digit (0 through 9) is represented by a 4-bit binary code.

- For example, the decimal number 93 is represented as:

$$9 \to 1001$$

,  $3 \to 0011$ , so 93 is 1001 0011 in BCD.

#### **Operations in BCD**

Arithmetic operations in BCD (addition, subtraction) are performed digit by digit. However, if the result of a digit addition exceeds 9 (1001 in binary), a correction must be applied:

• Correction Rule: If the sum of a digit exceeds 9, add 6 (0110 in binary) to that digit and propagate the carry to the next higher digit.

#### **Example of BCD Addition:**

Add 44 and 89 in BCD:

- Represent 44 as: 0100 0100

- $\bullet$  Represent 89 as:  $1000\ 1001$

- Add corresponding digits:

- $\circ$  Right nibble: 0100+1001=1101. Since 1101 (13) is greater than 9, add 0110 to get  $1101+0110=1\,0011$  (carry 1, result digit 0011).

- $\circ$  Left nibble:  $0100+1000+\mathrm{carry}\ 1=0100+1000+0001=1101.$  Again, 1101 (13) is greater than 9, so add 0110 to get  $1101+0110=1\ 0011$  (carry 1, result digit 0011).

- The final BCD result must be adjusted to reflect the carried digits appropriately. (The

exact BCD representation would depend on the method used, ensuring the final

answer has the correct number of significant digits based on the lowest precision

input.)

#### Importance of BCD

BCD is crucial in systems where decimal accuracy matters because it avoids rounding errors that can occur when converting between binary and decimal. Although it is less space-efficient than pure binary, its simplicity in representing decimal digits makes it valuable in financial and commercial applications.

## **Summary**

This note has covered:

- **Multiplication:** Both unsigned and signed (using two's complement), focusing on the shift-and-add method and the handling of sign bits.

- **Division:** Both unsigned (via shift-and-subtract) and signed division (including conversion to absolute values and sign correction).

- **Binary-Coded Decimal (BCD):** Representation of decimal digits in 4-bit groups, the rules for BCD arithmetic, and the importance of maintaining decimal precision.

Understanding these operations is essential for designing efficient digital systems, especially in contexts where arithmetic accuracy and data representation are critical.

# **Self Test**

**Self-Test: Lecture 3**

# 4. Combinational Digital Systems and Boolean Algebra

This note covers topics from combinational digital systems to Boolean algebra, as presented in the lecture slides (23 to 57). It includes detailed explanations of digital logic circuits, basic gate functions, multi-input systems, and key Boolean algebra theorems and properties.

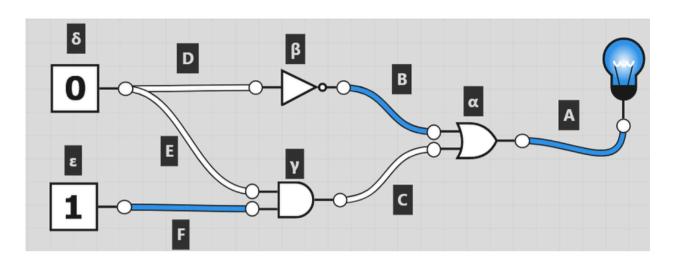

# **Combinational Digital Systems**

Combinational digital systems are circuits where the output depends solely on the current inputs, with no memory elements. They contrast with sequential systems, where past inputs affect the current output.

**COMBINATIONAL DIGITAL SYSTEM:** A system in which the output is determined only by the current combination of inputs.

#### **Key Points:**

- No storage or memory; all operations are instantaneous.

- Used for arithmetic operations, data routing, and signal processing.

• Fundamental building blocks for more complex circuits like adders, multiplexers, and decoders.

## Combinational Digital Systems

## **Logic Gates**

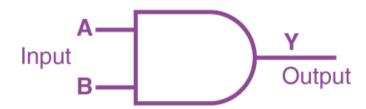

#### **AND Gate**

- Function: Outputs 1 only if both inputs are 1.

- $\bullet \ \ \text{Algebraic Expression:} \ f = x \cdot y$

#### • Truth Table:

| x | у | $x \cdot y$ |

|---|---|-------------|

| 0 | 0 | 0           |

| 0 | 1 | 0           |

| 1 | 0 | 0           |

| 1 | 1 | 1           |

**AND GATE:** A basic digital logic gate that produces an output of 1 if and only if all its inputs are 1.

@ Rvius com

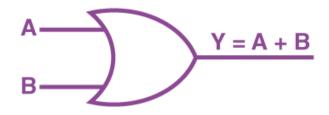

#### **OR Gate**

- Function: Outputs 1 if at least one input is 1.

- Algebraic Expression: f=x+y

- Truth Table:

| х | у | x + y |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 1     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

**OR GATE:** A logic gate that outputs 1 if one or more of its inputs are 1.

@ Bvius.com

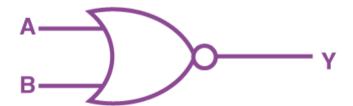

#### **NOR Gate**

• Function: Outputs 1 only if all inputs are 0 (i.e., the complement of OR).

$\bullet \ \ \hbox{Algebraic Expression:} \ f=(x+y),$

• Truth Table:

| х | у | f |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

**NOR GATE:** A logic gate whose output is the complement of the OR gate's output.

Bvius.com

#### **NAND Gate**

• Function: Outputs 0 only if all inputs are 1 (i.e., the complement of AND).

• Algebraic Expression:  $f = (x \cdot y)$

#### • Truth Table:

| X | у | f |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

**NAND GATE:** A gate that outputs the inverse of the AND gate's result.

Bvius.com

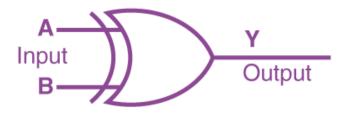

#### **XOR Gate**

- Function: Outputs 1 if the inputs are different.

- Algebraic Expression:  $f=x\oplus y=(x\cdot \overline{y})+(\overline{x}\cdot y)$

- Truth Table:

| х | у | f |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

**XOR GATE:** An exclusive OR gate that outputs 1 when the number of 1's in the inputs is odd.

@ Bvius.com

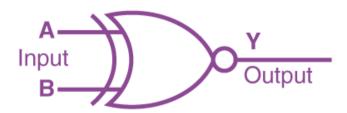

#### **XNOR Gate**

• Function: Outputs 1 if the inputs are the same.

• Algebraic Expression:  $f = (x \oplus y)$ '

• Truth Table:

| х | у | f |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

**XNOR GATE:** A gate that produces an output of 1 when both inputs are equal; it is the complement of the XOR gate.

@ Bvius.com

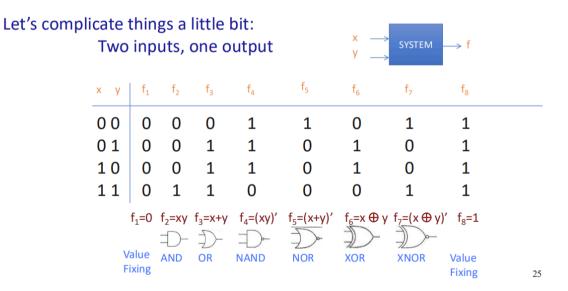

## **Combinational Digital Systems**

These systems are built using logic gates. They produce an output solely based on the current inputs.

- **Simple Two-Input Systems:** Basic circuits that perform operations like AND, OR, and XOR.

- **Multi-Input Systems:** Systems with more than two inputs can be built by combining two-input gates.

- Design Strategies:

- **Sum of Products (SoP):** Expresses the function as an OR of minterms.

- **Product of Sums (PoS):** Expresses the function as an AND of maxterms.

**COMBINATIONAL DIGITAL SYSTEM:** A circuit where the output is a function solely of the current input values, with no memory element.

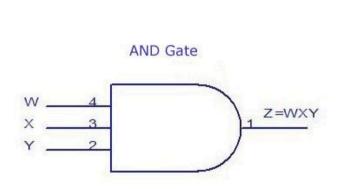

## **Three-Input Systems**

When designing systems with three or more inputs, the complexity increases, but the principles remain the same.

- **Example:** A three-input AND gate outputs 1 only when all three inputs are 1.

- **Design Consideration:** Ensure that the circuit is scalable by breaking down the logic into simpler two-input operations if necessary.

**THREE-INPUT SYSTEM:** A digital logic circuit that accepts three binary inputs and produces an output based on a specified Boolean function.

#### 3 Input AND Gate

| INPUTS |   |   | OUTPUT |

|--------|---|---|--------|

| W      | × | Y | Z      |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 0      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 0      |

| 1      | 0 | 0 | 0      |

| 1      | 0 | 1 | 0      |

| 1      | 1 | 0 | 0      |

| 1      | 1 | 1 | 1      |

TOUTU TABLE

## General Approach for Building Combinational Digital Systems

The design of combinational circuits generally follows these steps:

- Define the Boolean function using truth tables.

- Express the function in standard forms, such as SoP or PoS.

- Use Boolean algebra to simplify the expression.

- Implement the simplified expression using basic logic gates.

**DESIGN APPROACH:** Use Boolean algebra and standard forms (SoP or PoS) to design efficient combinational circuits from basic gates.

## **Boolean Algebra**

Boolean algebra is the mathematical foundation of digital logic. It uses a set of variables that take on values from  $\{0,1\}$  and is governed by specific operations and laws.

#### **Basic Operations**

- AND (⋅)

- OR (+)

- NOT (')

**BOOLEAN ALGEBRA:** A branch of algebra dealing with binary variables and logical operations.

| NO            | OT                                                                                                                                                                                                                                     |  | , | AND | ) |  |   | OR |   | , | XOF | <b>\</b> |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---|-----|---|--|---|----|---|---|-----|----------|

| X             | F                                                                                                                                                                                                                                      |  | X | У   | F |  | X | У  | F | Х | y   | F        |

| 0             | 1                                                                                                                                                                                                                                      |  | 0 | 0   | 0 |  | 0 | 0  | 0 | 0 | 0   | 0        |

| 1             | 0                                                                                                                                                                                                                                      |  | 0 | 1   | 0 |  | 0 | 1  | 1 | 0 | 1   | 1        |

|               |                                                                                                                                                                                                                                        |  | 1 | 0   | 0 |  | 1 | 0  | 1 | 1 | 0   | 1        |

| $\rightarrow$ | $\rightarrow$                                                                                                                                                                                                                          |  | 1 | 1   | 1 |  | 1 | 1  | 1 | 1 | 1   | 0        |

|               | $\Rightarrow \Rightarrow $ |  |   |     |   |  |   |    |   |   |     |          |

## **Boolean Algebra Theorems**

**Identities and Null Elements**

• Identity Laws:

$$x+0=x$$

and  $\mathbf{x}\cdot \mathbf{1}=x$

Null Laws:

$$x+1=1$$

and  $x\cdot 0=0$

**IDENTITY AND NULL LAWS:** Fundamental rules that simplify expressions by defining the effect of adding 0 or multiplying by 1, and their opposites.

### **Idempotency and Complements**

• Idempotent Laws:

$$x+x=x$$

and  $x\cdot x=x$

• Complement Laws:

$$x+x'=1$$

and  $x\cdot x'=0$

**IDEMPOTENCY:** The property that combining a variable with itself does not change its value.

**COMPLEMENT:** A variable's complement is the opposite value (if x=0, then  $x^\prime=1$ ; if x=1, then  $x^\prime=0$ ).

#### **Involution and Commutativity**

• Involution:

$$(x')' = x$$

• Commutativity:

$$x+y=y+x \text{ and } x\cdot y=y\cdot x$$

• Associativity:

$$x + (y + z) = (x + y) + z$$

and  $x \cdot (y \cdot z) = (x \cdot y) \cdot z$

**INVOLUTION:** The principle that taking the complement twice returns the original value.

| Name             | AND form                                      | OR form                                       |

|------------------|-----------------------------------------------|-----------------------------------------------|

| Identity law     | 1A = A                                        | 0 + A = A                                     |

| Null law         | 0A = 0                                        | 1 + A = 1                                     |

| Idempotent law   | AA = A                                        | A + A = A                                     |

| Inverse law      | $A\overline{A} = 0$                           | $A + \overline{A} = 1$                        |

| Commutative law  | AB = BA                                       | A + B = B + A                                 |

| Associative law  | (AB)C = A(BC)                                 | (A + B) + C = A + (B + C)                     |

| Distributive law | A + BC = (A + B)(A + C)                       | A(B+C) = AB + AC                              |

| Absorption law   | A(A + B) = A                                  | A + AB = A                                    |

| De Morgan's law  | $\overline{AB} = \overline{A} + \overline{B}$ | $\overline{A + B} = \overline{A}\overline{B}$ |

## **More Theorems and Distributive Properties**

• Distributive Laws:

$$x \cdot (y+z) = (x \cdot y) + (x \cdot z)$$

$$x + (y \cdot z) = (x+y) \cdot (x+z)$$

• Absorption Laws:

$$x + (x \cdot y) = x$$

$$x \cdot (x + y) = x$$

**DISTRIBUTIVE AND ABSORPTION LAWS:** Rules that allow the reorganization and simplification of Boolean expressions.

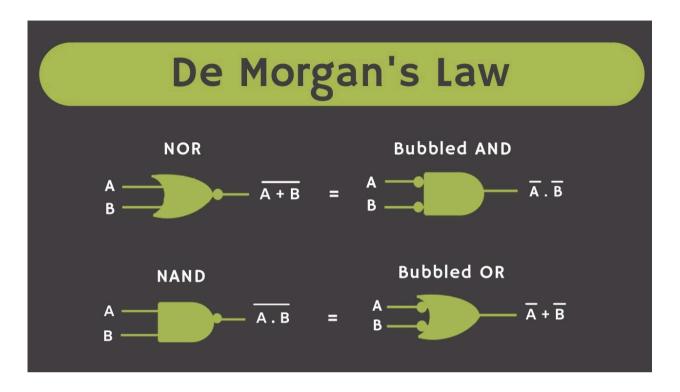

## **DeMorgan's Equivalences and Duality**

#### **DeMorgan's Equivalences**

•

$$(x \cdot y)' = x' + y'$$

$$\bullet \ \ (x+y)'=x'\cdot y'$$

**DE-MORGAN'S LAWS:** Fundamental transformations that allow the complement of a conjunction to be expressed as the disjunction of the complements, and vice versa.

#### **Duality Principle**

The duality principle states that every Boolean expression remains valid if you swap AND with OR and 0 with 1 throughout the expression.

**DUALITY:** The principle that the dual of any Boolean expression (by interchanging + and  $\cdot$ , and swapping 0 and 1) is also valid.

#### **Extension to N-Variable Theorems**

Boolean algebra extends naturally to functions of n variables:

Theorems such as:

$$(x_1+x_2+\cdots+x_n)'=x_1'\cdot x_2'\cdots x_n'$$

$$(x_1 \cdot x_2 \cdots x_n)' = x_1' + x_2' + \cdots + x_n'$$

• These generalize the two-variable cases to functions with many inputs.

**NOTE:** N-variable theorems are critical when designing complex digital circuits that involve multiple inputs.

## **Back to Our Earlier Example**

In earlier slides, a Boolean function was presented and simplified using the Sum of Products (SoP) approach. Although we are excluding the detailed minterm/maxterm representations beyond slide 57, it is important to understand that:

- **SoP (Sum of Products)** expresses a Boolean function as an OR of multiple AND terms.

- This method is widely used to implement digital circuits.

- The simplified expressions allow for efficient hardware implementations using basic gates.

**SUMMARY:** Using Boolean algebra, any Boolean function can be systematically simplified and implemented using a combination of logic gates, ensuring efficient digital circuit design.

## **Summary**

This study material has covered:

- **Combinational Digital Systems:** The basis of digital circuits with outputs depending solely on current inputs.

- **Logic Gates:** Detailed discussion of AND, OR, NOR, NAND, XOR, and XNOR gates, including their functions and truth tables.

- Multi-Input Systems: How combinational systems extend to three or more inputs.

- Design Approaches: Using Boolean algebra to express functions in standard forms such as Sum of Products (SoP) and Product of Sums (PoS).

- Boolean Algebra: Fundamental theorems, identities, and properties (including idempotency, complements, DeMorgan's Laws, duality, and distributivity).

- **Extension to N-Variable Functions:** Generalizing Boolean expressions for more complex systems.

Understanding these topics is crucial for designing and optimizing digital systems, as well as for simplifying and implementing logical functions in hardware.

## **Self Test**

## 5. Boolean Function Representations and Circuit Optimization

## **Objective & Scope**

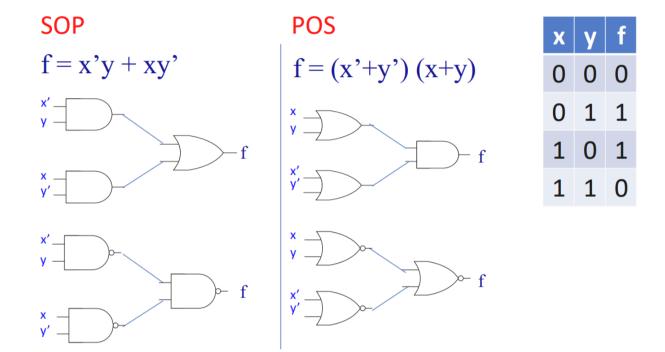

This note covers key topics from slides 14 to 49, focusing on methods to represent and optimize Boolean functions and digital circuits. Topics include:

- Sum of Products (SOP) and Product of Sums (POS) approaches

- Comparison between SOP and POS representations

- Standard forms using minterms and maxterms

- Alternative representations and algebraic simplifications

- Circuit optimization criteria such as literal cost and gate input cost

This note is designed to provide a clear, comprehensive understanding of these fundamental digital design concepts.

## Sum of Products (SOP) Approach

**SOP Approach:** A method of representing Boolean functions where the function is expressed as a sum (OR) of product (AND) terms, each called a minterm.

#### • Minterms:

**MINTERM:** A product term in which all variables appear exactly once (either complemented or uncomplemented). For a two-variable function, the minterms are:

#### • Example (Two-Input System):

Consider a function f defined by the truth table:

| x | у | f |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

This function can be represented as:

$$f = m_0 + m_1 + m_3$$

where each  $m_i$  is a minterm corresponding to the input combination.

## Example

$$f = m_0 + m_1 + m_3$$

$$f = x'y' + x'y + xy$$

$$x'$$

$$y'$$

$$x'$$

$$y$$

| х | У | f |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

## Product of Sums (POS) Approach

**POS Approach:** An alternative representation where the Boolean function is expressed as a product (AND) of sum (OR) terms. Each sum term is called a maxterm.

#### Maxterms:

**MAXTERM:** A sum term that contains every variable exactly once (in complemented or uncomplemented form). For a two-variable function, the maxterms are:

$$X + Y$$

,  $X + Y'$ ,  $X' + Y$ ,  $X' + Y'$

#### • Example (Two-Input System):

For a function defined by:

| х | у | f |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

The POS representation may be obtained by first determining the maxterms for the outputs that are 0 and then forming the product.

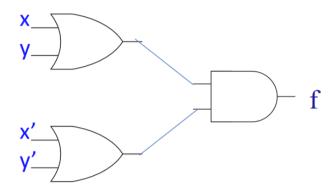

- · Going back to the XOR function

- Apply the bubble trick!

$$f = (x+y) \cdot (x'+y')$$

| х | у | f |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

## **SOP vs. POS Representations**

- Comparison:

- **SOP (Sum of Products):** Uses minterms; generally leads to an OR of AND terms.

- **POS (Product of Sums):** Uses maxterms; results in an AND of OR terms.

**Key Observation:** For any Boolean function, the SOP and POS representations are duals of each other. The duality can be obtained by swapping ANDs with ORs, 0's with 1's, and variables with their complements.

#### • Example (XOR Function):

The XOR function can be expressed in SOP form as:

$$f = x'y + xy'$$

Its equivalent POS form can be derived as:

$$f = (x + y) \cdot (x' + y')$$

This dual representation is useful when designing circuits using only NAND or NOR gates.

### Standard Forms: Minterms and Maxterms

#### • Minterms:

- $\circ$  There are  $2^n$  minterms for an n-variable function.

- $\circ\;$  Every Boolean function can be expressed as the sum of its minterms.

- o Missing minterms correspond to the complement function.

#### • Maxterms:

- $\circ$  There are  $2^n$  maxterms for an n-variable function.

- Every Boolean function can also be represented as the product of its maxterms.

- o A function that includes all maxterms equals 0.

Standard Form Representations: A canonical SOP expression is written as  $f=\Sigma m(i)$ , while a canonical POS expression is written as  $f=\Pi M(i)$ .

#### • Example (Three-Variable Function):

For a function F(x, y, z), one might have:

$$F = x'y'z' + x'yz' + xy'z + xyz$$

and its complement can be expressed using maxterms.

## Alternative Representations and Algebraic Simplification

#### • Algebraic Simplification:

Boolean algebra theorems (e.g., absorption, DeMorgan's laws) are used to reduce expressions, which directly leads to simplified circuits.

#### Absorption Law Examples:

$$X + XY = X$$

and  $X(X + Y) = X$

#### DeMorgan's Equivalences:

$$(X \cdot Y)' = X' + Y'$$

and  $(X + Y)' = X' \cdot Y'$

#### • Applying the Bubble Trick:

A technique to derive the POS form from a given SOP form by complementing and then re-complementing the function.

#### • Canonical to Simplified Form:

Starting with a canonical sum (or product) and then applying algebraic methods to minimize the literal count, which directly impacts circuit cost.

## Circuit Optimization: Literal and Gate Input Cost

#### Optimization Goals:

Minimize the hardware cost (number of gates and inputs) while ensuring correct logical functionality.

#### • Literal Cost (L):

**LITERAL COST:** The total number of literal appearances (variables and their complements) in a Boolean expression.

#### • Gate Input Cost (G):

**GATE INPUT COST:** The total number of inputs to the gates used in the circuit implementation. Sometimes, the cost with NOT gates is also considered (GN).

#### • Example:

For a circuit implementing

$$F = BD + AB'C + AC'D'$$

the literal cost might be 8 if each variable appearance is counted. Gate input cost is calculated by summing the inputs for each gate used.

#### • Choosing the Best Implementation:

A lower literal and gate input cost often means a simpler, more efficient circuit. Designers may choose between alternative representations (SOP vs. POS) based on these cost criteria.

## Cost Criteria - Example

$$L = 6$$

$$G = 6 + 2 = 8$$

$$GN = 8 + 3 = 1$$

•

$$F = (A + C')(B' + C)(A' + B)$$

$$L = 6$$

$$G = 6 + 3 = 9$$

$$GN = 9 + 3 = 12$$

•  $F = \overrightarrow{A} \overrightarrow{B} \overrightarrow{C} + \overrightarrow{A'} \overrightarrow{B'} \overrightarrow{C'}$

## Final Summary & Key Takeaways

#### • Representation Methods:

- **SOP** uses minterms and provides an OR of AND terms.

- **POS** uses maxterms and provides an AND of OR terms.

#### • Duality and Equivalence:

Understanding the duality between SOP and POS forms helps in converting and optimizing Boolean expressions.

#### Standard Forms:

Canonical forms using minterms and maxterms provide a systematic way to represent any Boolean function, serving as a starting point for simplification.

#### • Circuit Optimization:

Techniques such as algebraic simplification, the bubble trick, and cost analysis (literal and gate input cost) are crucial for designing efficient digital circuits.

This comprehensive note consolidates the key points from slides 14 to 49, equipping you with the foundational knowledge to represent and optimize Boolean functions for digital circuit design.

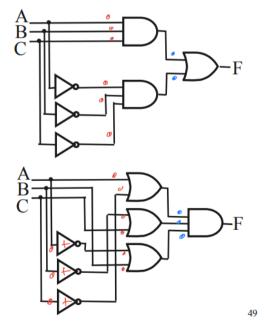

# 6. Karnaugh Maps and Boolean Function Optimization

## **Objective & Scope**

This note covers the use of Karnaugh Maps (K-maps) and related techniques for optimizing Boolean functions and digital circuits. It focuses on:

- Understanding the basic structure and purpose of K-maps

- Using two-variable and three-variable K-maps for function representation

- Alternative map labeling for improved pattern recognition

- Combining squares (grouping) to simplify Boolean expressions

- Practical examples of K-map simplification and circuit optimization

This comprehensive note is intended to provide both the theoretical foundations and practical applications needed for effective digital circuit design.

## **Karnaugh Maps (K-maps)**

**Karnaugh Map (K-map):** A graphical tool that reorganizes a Boolean function's truth table into a grid format where adjacent cells differ by only one variable. This structure

enables visual grouping (combining) of 1's to simplify Boolean expressions.

#### • Structure:

- o Composed of squares, each representing a minterm.

- Cells are arranged so that adjacent ones (horizontally or vertically) differ by a single bit (Gray code ordering).

- o Can be viewed as a reorganized truth table or a warped Venn diagram.

## **Uses of Karnaugh Maps**

#### **Key Uses:**

- **Simplification:** Derive optimum or near-optimum SOP (Sum of Products) or POS (Product of Sums) expressions.

- **Optimization:** Minimize the literal cost and gate input cost in circuit implementations.

- **Visualization:** Make the relationships between minterms clear, thereby aiding in the identification of simplification opportunities.

- **Design:** Serve as an instructive tool for manually optimizing small digital circuits before applying computer-aided techniques.

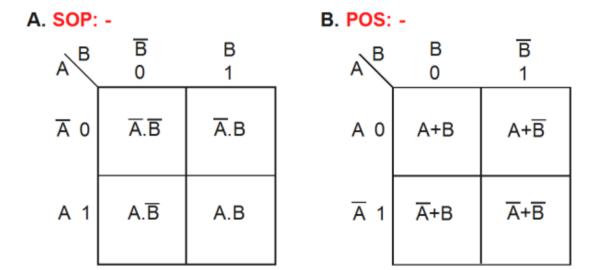

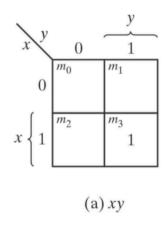

## Two-Variable K-Maps

#### • Basic Layout:

$\circ$  A 2-variable K-map has 4 cells corresponding to the minterms for variables x and y:

$\blacksquare$   $m_0: x'y'$

$\blacksquare$   $m_1: x'y$

$\blacksquare$   $m_2:xy$

$\blacksquare$   $m_3:xy$

#### • Adjacency:

- Cells adjacent either horizontally or vertically differ by only one variable.

- This property allows adjacent cells containing 1's to be grouped for simplification.

## Two Variable K-Maps

- Minterm m<sub>0</sub> and minterm m<sub>1</sub> are "adjacent"

- They differ in the value of the variable y

- Similarly,

- Minterms  $\mathbf{m}_0$  and  $\mathbf{m}_2$  differ in the  $\mathbf{x}$  variable

- Minterms m<sub>1</sub> and m<sub>3</sub> differ in the x variable

- $-\,$  Minterms  $\mathbf{m_2}$  and  $\mathbf{m_3}$  differ in the  $\mathbf{y}$  variable

|       | y = 0                  | y = 1                 |

|-------|------------------------|-----------------------|

| x = 0 | m <sub>o</sub><br>x'y' | m <sub>1</sub><br>x'y |

| x = 1 | m <sub>2</sub><br>xy'  | m <sub>3</sub><br>xy  |

## K-Maps and Truth Tables

#### • Relationship:

• A K-map is simply a reordering of a truth table to expose adjacent minterm groupings.

• This organization helps in directly translating truth table information into simplified Boolean expressions.

#### • Representation:

- Values from a truth table are entered into the K-map, marking 1's for minterms where the function is true.

- These marked cells are then grouped to form simplified product terms.

| Input<br>Values | Function<br>Value<br>F(x,y) |

|-----------------|-----------------------------|

| (x,y)<br>0 0    | a a                         |

| 01              | b                           |

| 10              | c<br>d                      |

|                  | y = 0 | y = 1 |

|------------------|-------|-------|

| $\mathbf{x} = 0$ | a     | b     |

| x = 1            | c     | d     |

## K-Map Function Representation

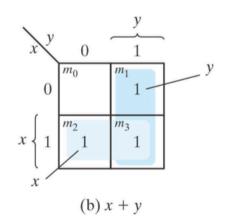

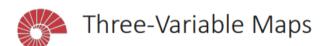

## Three-Variable K-Maps

#### • Layout:

• A 3-variable K-map contains 8 cells.

- The arrangement is designed so that each cell is adjacent to those that differ by a single variable change.

- o Commonly, variables are ordered such that one dimension (e.g., rows) represents one variable while columns represent the other two in Gray code order.

#### • Adjacency in 3-Variable Maps:

- Allows grouping of cells into rectangles containing 2, 4, or 8 cells (powers of 2) for minimization.

- The map can be visualized as a cylinder or a torus where the edges wrap around, preserving adjacency.

## Three Variable Maps

A three-variable K-map:

Note that if the binary value for an <u>index</u> differs in one-bit position (Gray code sequence), the minterms are adjacent on the K-Map

## Alternative Map Labeling

**Alternative Labeling:** Adjusting the labels or ordering of variables in a K-map can make certain groups more apparent. This includes:

- Changing the sequence of variable representation.

- Using different orientations to emphasize adjacent groupings.

#### • Purpose:

o Facilitates easier identification of common patterns.

• Enhances clarity in reading product terms from the map.

## **Combining Squares (Grouping)**

#### • Concept:

- **Grouping:** The process of combining adjacent 1's (marked cells) in the K-map to form larger rectangles.

- **Goal:** Reduce the number of literals (variables) in each product term.

#### • Grouping Guidelines:

- Single Cell: Represents a minterm with all variables.

- Pair of Adjacent Cells: Can eliminate one variable.

- **Four Adjacent Cells:** Can reduce a term to a single variable or even represent a constant.

- **Edge Wrapping:** Cells on the edges of the K-map are considered adjacent if they wrap around.

• Topological warps of 3-variable K-maps that show all adjacencies:

## Final Summary & Key Takeaways

- **Karnaugh Maps (K-maps)** are powerful tools for Boolean function optimization, particularly effective for functions with a small number of variables.

- **Two-variable and three-variable maps** provide a structured method for visualizing and simplifying Boolean expressions.

- **Grouping (combining squares)** reduces the number of literals in product terms, thereby minimizing circuit complexity.

• Alternative labeling and visualization techniques help in recognizing patterns and adjacencies that may not be immediately obvious.

#### • Practical Applications:

K-maps are used to derive simplified SOP and POS forms, which lead to lower literal and gate input costs in digital circuit implementations.

This note consolidates the key concepts from slides 51 to 67, equipping you with a clear understanding of how to apply K-map techniques for Boolean function optimization in digital system design.

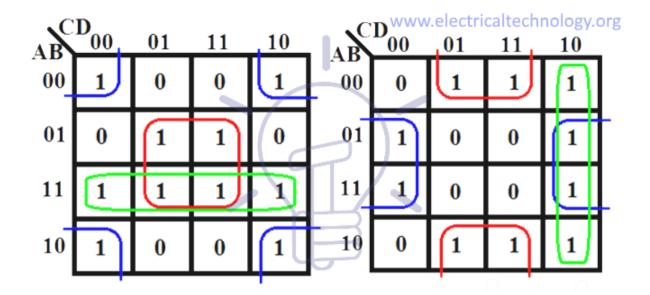

## 7. Karnaugh Map Simplification & Prime Implicant Optimization

## **Objective & Scope**

This note focuses on methods for simplifying Boolean functions using Karnaugh maps (K-maps) and optimizing their representations through prime implicants. We cover techniques for three-variable and four-variable K-maps, learn how to identify minterms and maxterms, practice prime implicant extraction, and explore an optimization algorithm to select a cost-effective solution. This material corresponds to slides 15 to 23.

## Three-Variable Map Simplification

#### Overview:

The goal is to use a 3-variable K-map to simplify a Boolean function by grouping adjacent 1's.

#### Key Concepts:

- Grouping adjacent cells in powers of 2 (1, 2, 4, ...) minimizes the number of literals in the product terms.

- o Simplified terms (prime implicants) are derived from these groups.

**Simplification Principle:** Group adjacent 1's in the K-map to form the largest possible rectangles; each rectangle corresponds to a product term with fewer variables.

## Three-Variable Map Minterms/Maxterms

#### Minterms and Maxterms:

- Minterm: A product term where every variable appears exactly once (in true or complemented form).

- Maxterm: A sum term that includes every variable exactly once.

#### • Usage in K-maps:

Minterms are used in the Sum of Products (SOP) representation; maxterms are used in the Product of Sums (POS) representation.

#### • Example:

A function may be written as a sum of specific minterms extracted from the K-map, or as a product of its maxterms.

**Key Idea:** Expressing a function in canonical form provides a starting point for minimization via grouping.

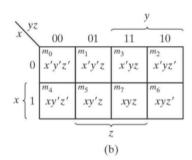

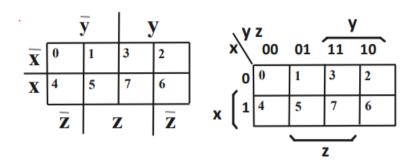

## Four-Variable Maps

#### Introduction to Four-Variable K-Maps:

Four-variable K-maps extend the principles of 3-variable maps with 16 cells.

#### • Layout and Adjacency:

- o Cells are arranged so that every adjacent pair differs by only one variable.

- Enables grouping of 1's into larger rectangles (groups of 2, 4, 8, or 16).

**Note:** Understanding four-variable maps is essential for functions of higher complexity, as the same grouping principles apply.

F(A,B,C,D)

#### Four Variable Terms

#### • Definition:

A "term" in a Boolean expression derived from a four-variable K-map.

#### • Grouping Effects:

- A single cell represents a minterm with 4 literals.

- o A pair (2 cells) reduces one variable (3 literals remain).

- o A group of four cells results in a term with 2 literals.

- o Larger groups (e.g., eight cells) can reduce the term to a single literal.

#### • Optimization Impact:

Grouping reduces the literal count, lowering both the complexity and the hardware cost of the resulting circuit.

**Optimization Tip:** Always look for the largest possible grouping to minimize the expression.

## Karnaugh-map Usage

#### • Procedure for Using K-Maps:

$\circ~$  Plot the function's output (1's for true minterms) into the K-map.

- Circle or highlight the largest rectangular groups of 1's (the groups must contain 2^n cells).

- Translate each group into its corresponding product term.

#### Benefits:

- Reduces the number of terms and literals.

- Provides a visual method for function minimization.

**Usage Guidelines:** The groups (or prime implicants) must cover all 1's in the map, and overlapping groups can sometimes yield a more optimal solution.

## **Example of Prime Implicants**

#### • Prime Implicant:

A group (rectangle) on the K-map that cannot be combined with adjacent groups to form a larger group.

#### Identification:

- Mark all groups of 1's.

- o Identify which groups cover 1's that no other group covers (these are essential prime implicants).

#### • Example Process:

For a given function on a 3-variable or 4-variable map, list all potential groups and then narrow them down to prime implicants based on their coverage and size.

**Remember:** Prime implicants are the building blocks of a minimized Boolean expression.

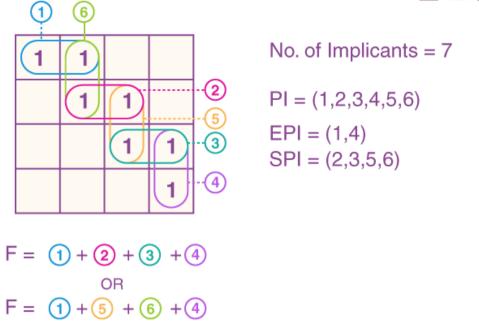

## **Optimization Algorithm**

#### • Optimization Process:

- 1. **Find all prime implicants:** List every possible grouping on the K-map.

- 2. **Identify essential prime implicants:** Determine which groups cover minterms uniquely.

- 3. **Select a minimum cost set:** From the remaining non-essential prime implicants, choose the ones that cover all minterms with the lowest overall cost (considering literal and gate input costs).

#### • Selection Rule:

- o Minimize overlap among selected prime implicants.

- Ensure each chosen prime implicant includes at least one minterm not covered by another.

#### • Goal:

Obtain a simplified Boolean expression that minimizes hardware implementation cost.

**Optimization Insight:** The algorithm ensures that the final solution is not only logically correct but also cost-effective in practical circuit design.

## Final Summary & Key Takeaways

- Karnaugh Maps are a powerful graphical tool for Boolean function simplification.

- **Grouping in K-maps** reduces the number of literals in an expression, which directly lowers the complexity and cost of digital circuits.

- Prime Implicants represent the core simplified groups that cannot be further combined.

- **Optimization Algorithms** help select the best combination of prime implicants, balancing coverage and cost.

This note consolidates the key points from slides 15 to 23, offering a clear pathway from K-map simplification to prime implicant optimization for effective Boolean function reduction.

# 8. Digital Logic Optimization and Karnaugh Map Techniques

#### Introduction

Digital systems often require optimized logic circuits to reduce complexity, lower manufacturing costs, and improve performance. Simplification techniques such as Karnaugh maps (K-maps) help transform complex Boolean functions into simpler, more cost-effective forms. By applying systematic methods for grouping minterms and leveraging selection rules, designers can minimize the number of required logic gates and inputs.

## **Selection Rules and Prime Implicants**

The foundation of K-map optimization lies in identifying **prime implicants**—groups of adjacent 1s (minterms) that can be combined to form simplified product terms. A key strategy involves:

- Choosing prime implicants that minimize overlap: Each selected implicant should cover at least one minterm not shared with any other implicant.

- **Ensuring minimal literal cost:** The goal is to reduce the number of literals (variables or their complements) in each product term, thus lowering the overall gate input

This selection rule is critical for deriving a final expression that is both optimal and implementable with fewer gates.

#### Simplifying Four-Variable Functions

For functions defined over four variables, the Karnaugh map provides a clear visual tool to group minterms:

- **Grouping Adjacent Minterms:** By forming groups (or rectangles) that contain 2, 4, or 8 cells, the number of literals in each resulting product term is reduced.

- Extracting Simplified Expressions: Depending on how the groups are formed, you can derive either a Sum-of-Products (SOP) or a Product-of-Sums (PoS) expression.

The process involves visually identifying the largest possible groups that cover all 1s in the map while avoiding unnecessary overlap.

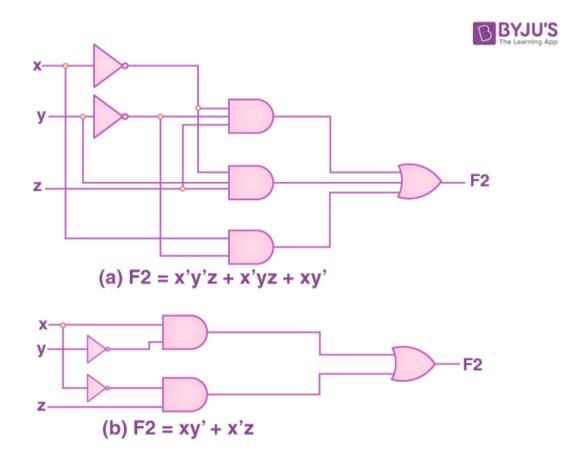

#### Converting to Product-of-Sums (PoS)

When a design requires a Product-of-Sums form—often for specific gate implementations like NOR-only circuits—the following steps are used:

- **Derive the Complement:** First, express the complement of the function in SOP form.

- Apply De Morgan's Law: Complement the expression to convert it into PoS form.

This approach yields a PoS expression that can simplify the circuit design by reducing the number of required gate inputs.

#### **Techniques for Functions with More Variables**

As functions grow to five or more variables, Karnaugh maps become more complex. To manage this:

• **Partition the Map:** Divide the map into sections based on the value of one or more variables. For example, a five-variable function may be split into two four-variable maps corresponding to a variable being 0 or 1.

• **Apply Standard Grouping:** Within each partition, the usual grouping techniques are used to combine adjacent minterms.

This segmentation enables the application of familiar two-level optimization techniques even for higher-variable functions.

#### **Incorporating Don't Care Conditions**

In many practical designs, certain input combinations never occur or their outputs are irrelevant. These are marked as **don't care conditions**:

- **Flexible Grouping:** Don't cares can be treated as either 0 or 1 in the K-map, allowing for larger groups that reduce the overall literal count.

- **Cost Reduction:** By including don't care cells in groups, the final logic expression often has fewer terms and lower gate input cost.

For example, in a BCD (Binary-Coded Decimal) circuit, only the codes 0000 to 1001 are valid. The remaining combinations (1010 to 1111) are don't cares, which can be used to simplify the circuit.

#### **Optimized Selection with Don't Cares**

Integrating don't care conditions into the selection process further enhances optimization:

- Larger Prime Implicants: By including don't care cells, groups can be expanded, which simplifies the final expression.

- **Minimized Overlap:** The selection rule is applied with the additional flexibility of choosing groups that cover both required minterms and don't care conditions.

This method leads to a design with even lower gate input costs and reduced overall complexity.

#### **Practical Application: 4-Bit Prime Number Detector**

One practical application of these optimization techniques is the design of a 4-bit prime number detector:

• **Function Definition:** The detector identifies prime numbers by outputting a high signal when the 4-bit input corresponds to a prime number.

- **Mapping Minterms:** The function is defined by minterms corresponding to prime numbers (e.g., 2, 3, 5, 7, 11, 13). Using a K-map, these minterms are grouped and simplified.

- **Resulting Expression:** The final simplified expression requires fewer gates, making the detector both efficient and cost-effective.

#### Practical Application: 4-Bit BCD Prime Number Detector

Adapting a prime number detector for BCD inputs requires additional considerations:

- **Valid Input Range:** BCD inputs range from 0000 to 1001, so the K-map is constructed only for these values.

- Handling Don't Cares: Inputs outside the valid range (typically 1010 to 1111) are marked as don't cares. These conditions are used to simplify the grouping on the Kmap.

- **Optimized Design:** The resulting logic function is simpler, ensuring the detector works accurately within the decimal range while using minimal hardware resources.

#### **Advanced Optimization Algorithms**

The process of Boolean function optimization can be summarized by the following steps:

- **Identify All Prime Implicants:** List every possible grouping of adjacent 1s in the K-map.

- **Determine Essential Prime Implicants:** Select those groups that cover minterms which no other group covers.

- **Select a Minimal Cover:** Choose a combination of prime implicants that covers all required minterms with minimal overlap.

- Calculate Gate Input Cost: Evaluate the final expression in terms of the number of gate inputs required, aiming to minimize this cost.

These steps ensure that the final implementation is both optimal and efficient, balancing simplicity with functionality.

#### Conclusion

Karnaugh map techniques are vital for simplifying Boolean functions in digital circuit design. By carefully applying selection rules, managing don't care conditions, and optimizing groupings in both SOP and PoS forms, designers can create circuits that are not only functionally correct but also cost-effective and efficient. These methods underpin many modern digital systems, contributing to better performance and reduced resource usage in practical applications.

# 9. Exclusive OR, Adder Circuits, and Digital Addition

#### **Exclusive OR (XOR) Fundamentals**

**XOR:** The Exclusive OR (XOR) operation outputs true only when the inputs differ. Its Boolean expression is given by:

$$F = X \cdot Y' + X' \cdot Y$$

#### • Truth Table:

| X | Υ | $X \oplus Y$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

Remark: Some useful identities of XOR include:

•

$$X \oplus 0 = X$$

- $X \oplus X = 0$   $X \oplus Y = Y \oplus X$   $X \oplus 1 = X$

- Associativity:  $(X \oplus Y) \oplus Z = X \oplus (Y \oplus Z) = X \oplus Y \oplus Z$

Remember Exclusive-OR or XOR gate?

| Γ. | $-\Delta$ | \ I |

|----|-----------|-----|

|    |           |     |

|    |           |     |

|    |           |     |

| X | Υ | X⊕Y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

#### **Applications of XOR in Digital Logic**

#### Binary Addition and the Half Adder

HALF ADDER: A half adder is a digital circuit that adds two one-bit binary numbers. It uses an XOR gate to compute the sum and an AND gate to generate the carry.

#### • Equations:

o Sum:

$$S = A \oplus B$$

o Carry:

$$C = A \cdot B$$

#### • Truth Table for Half Adder:

| Α | В | $S=A\oplus B$ | $C = A \cdot B$ |

|---|---|---------------|-----------------|

| 0 | 0 | 0             | 0               |

| 0 | 1 | 1             | 0               |

| 1 | 0 | 1             | 0               |

| 1 | 1 | 0             | 1               |

#### Use of XOR Gate

#### Consider Binary Addition of Two One-Bit Numbers

| Α      | Α | В | С             | S |

|--------|---|---|---------------|---|

|        | 0 | 0 | 0             | 0 |

| + B    | 0 | 1 | 0             | 1 |

| C S    | 1 | 0 | 0             | 1 |

|        | 1 | 1 | 1             | 0 |

| A<br>B | s |   | Half<br>Adder |   |

S=A ⊕ B

C=A B

#### **Extending XOR to Multi-Input Functions**

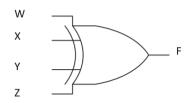

**MULTI-INPUT XOR:** A multi-input XOR gate computes the parity (odd or even) of its inputs. For example, a 3-input XOR function is defined as:

$$F = X \oplus Y \oplus Z$$

and can be implemented as  $(X \oplus Y) \oplus Z$ .

#### Properties:

• The output is 1 if an odd number of inputs are 1 (odd function).

13

- For a 4-input XOR, the output is 1 if the number of ones is odd.

- The Exclusive-NOR (XNOR) function is the complement of XOR and outputs true when the number of ones is even.

**Remark:** Multi-input XOR functions are widely used for parity checking and error detection, although they may incur longer delay lines in large-scale implementations.

#### Extending 2 input XOR gate to 3 input XOR gate

F= X⊕ Y ⊕Z F= (X⊕ Y) ⊕Z

**Checker Board Pattern!**

F = XY'Z' + X'Y Z' + XYZ + X'Y' Z

15

#### How about 4 input XOR gate

$F=W \oplus X \oplus Y \oplus Z$

$F=(W \oplus X \oplus Y) \oplus Z$

**Checker Board Pattern Again!**

**XOR= Odd Function**

| wx | YZ | 00 | 01 | 11 | 10 |

|----|----|----|----|----|----|

|    | 00 | 0  | 1  | 0  | 1  |

|    | 01 | 1  | 0  | 1  | 0  |

|    | 11 | 0  | 1  | 0  | 1  |

|    | 10 | 1  | 0  | 1  | 0  |

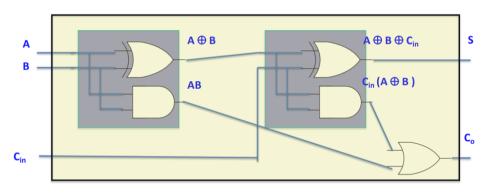

#### **Full Adder Circuit**

**FULL ADDER:** A full adder is a digital circuit that adds three bits (two significant bits and an input carry) to produce a sum and an output carry.

#### • Equations:

o Sum:

$$S = (A \oplus B) \oplus C_{in}$$

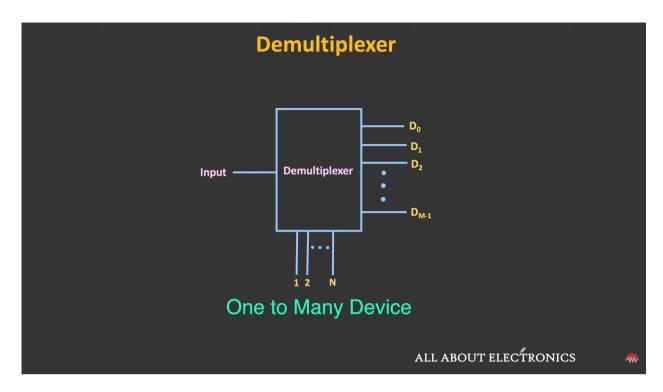

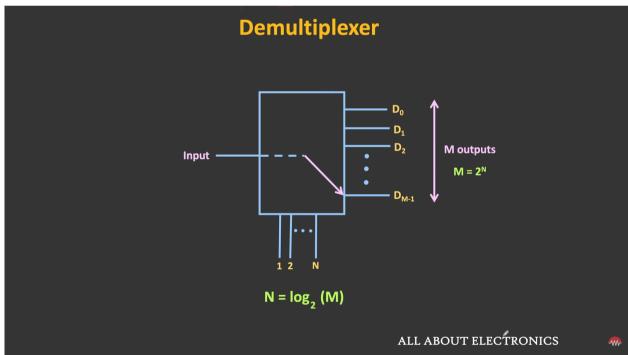

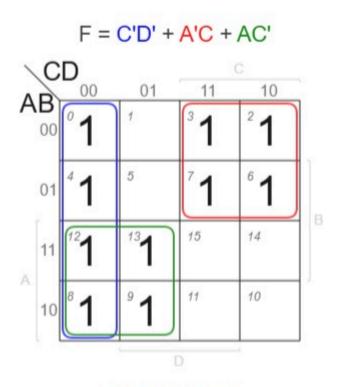

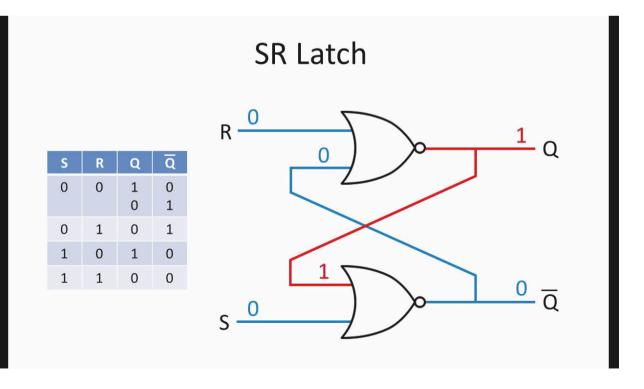

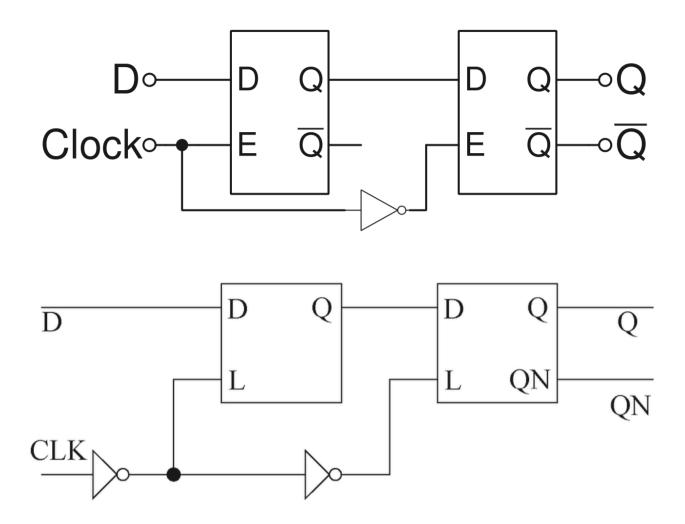

o Carry-out: